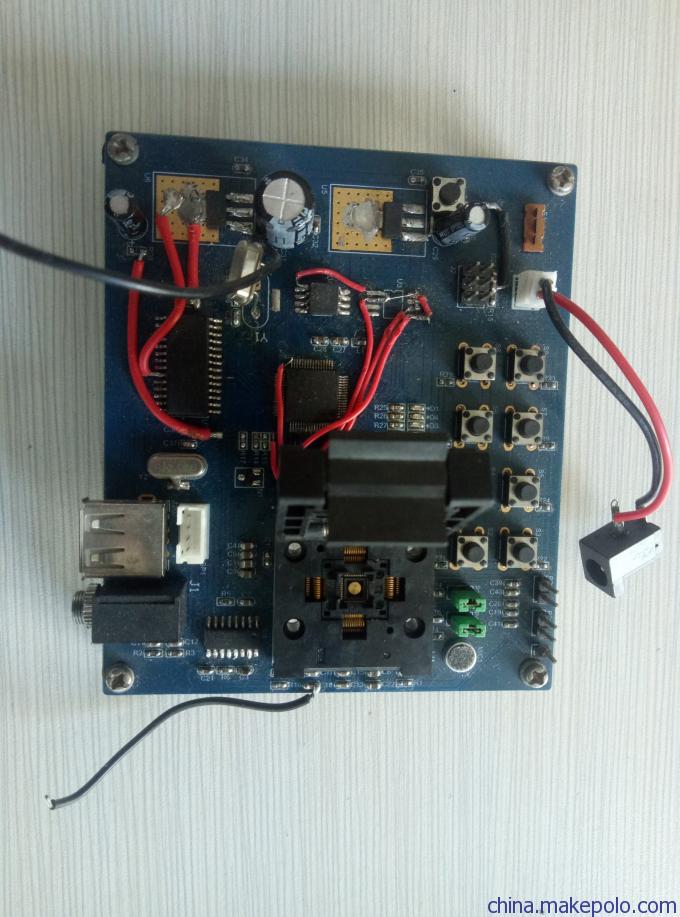

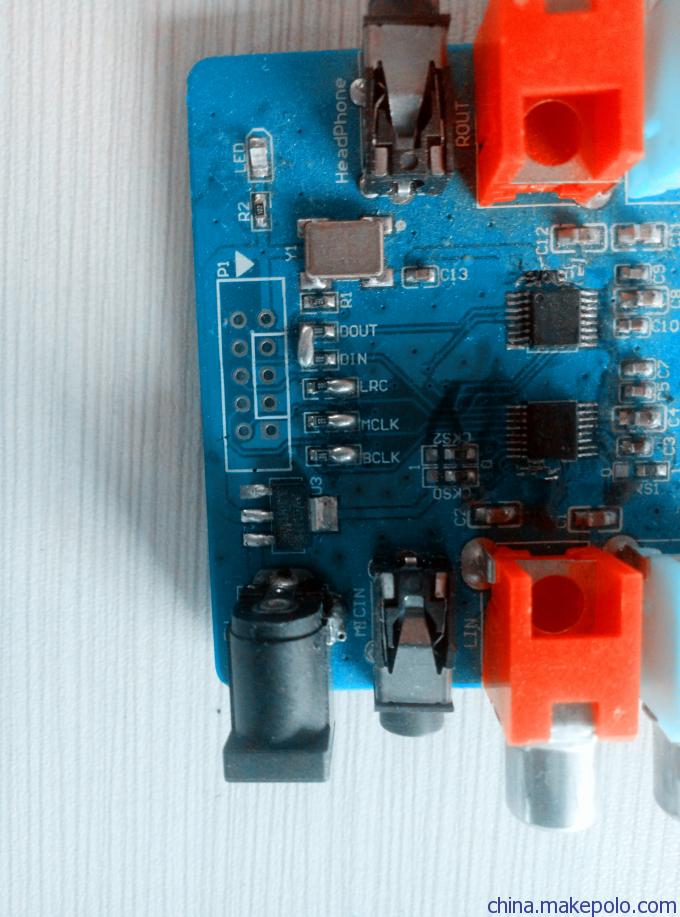

供应箓华CJC5340兼容CS5340模拟转数字音频

深圳市锦宏世纪科技有限公司

中国 深圳

产品属性

图文详情

品牌推荐

品牌

CJC

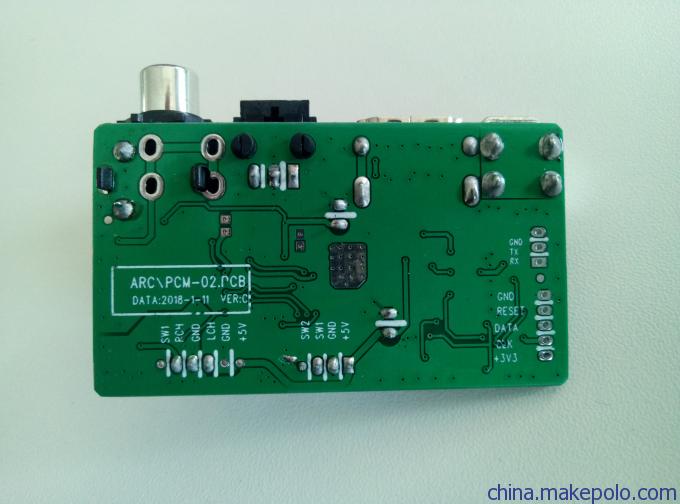

型号

CJC5340

批号

2018+

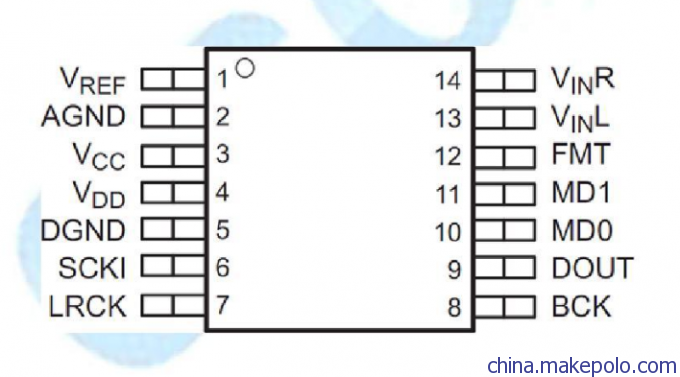

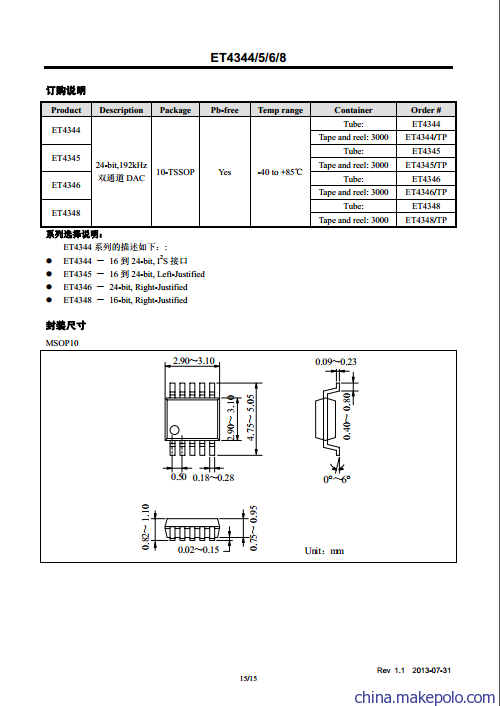

封装形式

SMD

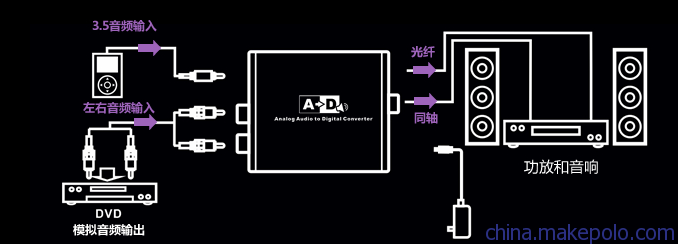

类型

数字集成电路

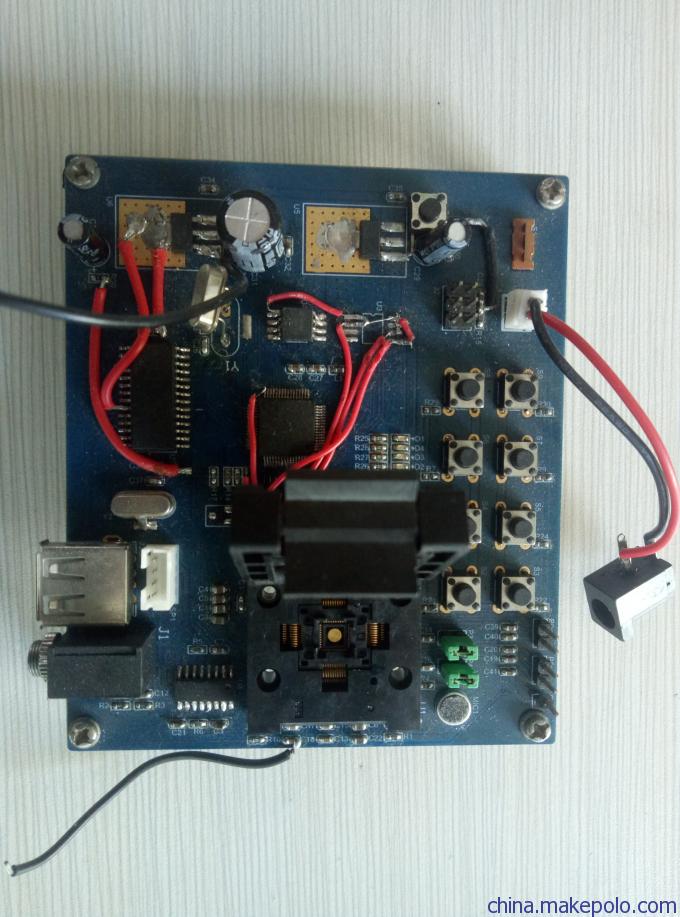

用途

电视机

功能

逻辑电路

导电类型

双极型

封装外形

扁平型

集成度

中规模50~100

工作电源电压

3.3V

最大功率

0.3W

工作温度

24bit℃

外形尺寸

QFN16mm

加工定制

加工定制

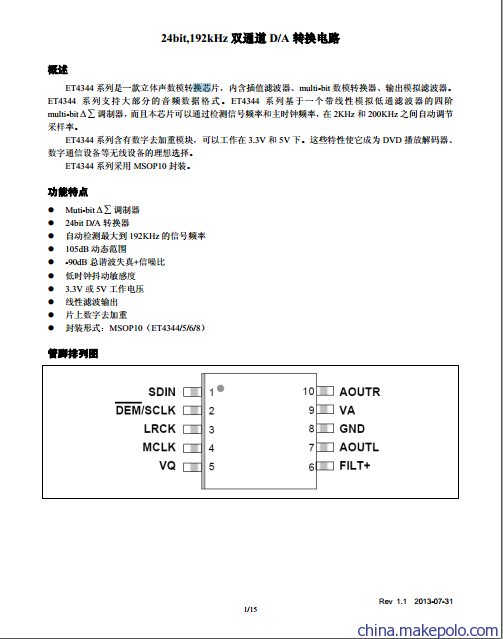

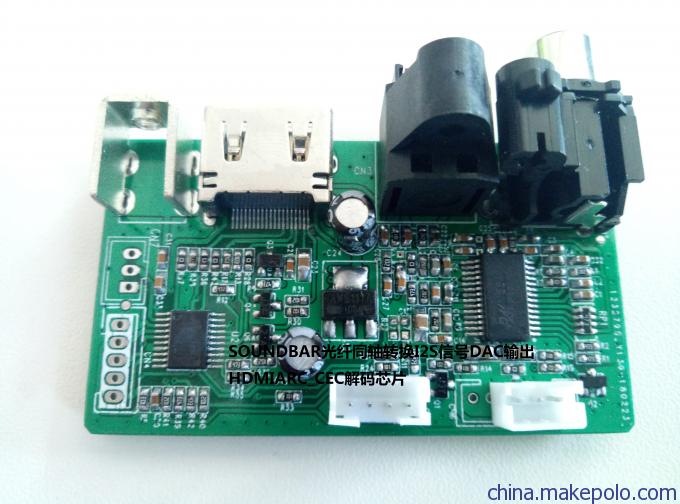

调制器

Muti-bit

转换器

24bit A/D

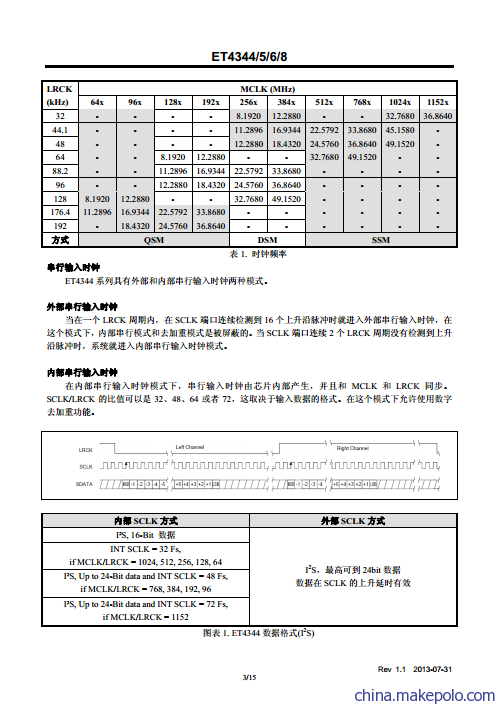

信号频率

自动检测最大到 192KHz

动态范围

105dB

总谐波失真+信噪比

-90dB