EPM240T100C5N代理

EPM240T100C5

EPM240T100C5N

EPM240T100C5N理

EPM240T100C5N中文资料 直线:13316887805 QQ:2501633055 范小姐

品牌 代理 价格 中文资料 引脚功能 封装 原理图 参数厂家等欢迎来电咨询!

EPM240T100C5N产品简介

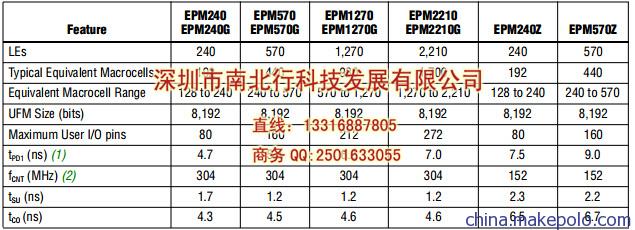

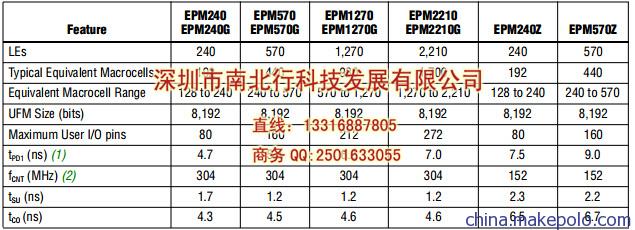

EPM240T100C5N即时在MAXIICPLD®家庭,非易失性是基于0.18µM,6-layer-metal-flash过程,密度从240到2210的逻辑单元(LE)(128至2210的等效宏单元)和8个千位的非易失性存储器。MAXII器件提供高I/O计数,快速高效,可靠的拟合与CPLD的架构。具有multivolt核心,用户闪存(UFM)块,和增强的在系统可编程(ISP),MAXII器件的设计,以降低成本和功率而应用如总线桥接提供可编程解决方案,I/O扩展,上电复位(POR)和顺序控制,和控制装置的配置。

EPM240T100C5N引脚功能

EPM240T100C5N MAX II CPLD具有以下特点:

■低成本,低功耗CPLD

■即时的,非易失性建筑

■待机电流低至25µ一

■提供快速的传播延迟和时钟的输出时间

■提供全球四时钟每两个时钟可用逻辑阵列块(实验室)

■UFM块达8千位的非易失性存储器

■multivolt核心使外部电源电压为3.3V/2.5V或1.8V的装置

■MultiVolt输入/输出接口支持3.3V,2.5V,1.8伏,和1.5-V逻辑电平

■总线友好的架构包括可编程转换率,驱动强度,总线,和可编程的上拉电阻

■施密特触发器使噪声容限输入(可编程每针)

■I/O是完全兼容的外围组件互连(PCISIG)的特殊利益集团的PCI局部总线规范2.2修订为3.3V的操作,在66兆赫

■支持热插拔

■建于联合测试行动小组(JTAG)边界扫描测试(BST)电路符合IEEE标准1149.1-1990

有关EPM240T100C5N理、EPM240T100C5N中文资料、EPM240T100C5N应用电路、EPM240T100C5N引脚功能、EPM240T100C5N工作温度、EPM240T100C5N型号封装、EPM240T100C5N PDF、EPM240T100C5N价格、EPM240T100C5N厂家图片、EPM240T100C5N现货供应信息,EPM240T100C5N理厂家品牌供应采购价格货源资料数量封装批号参数等欢迎来电咨询!

深圳市南北行科技发展有限公司

联系人:范小姐

直线:13316887805

商务QQ:2501633055